The MSI MEG Z390 ACE Motherboard Review: The Answer To Your USB 3.1 Needs

by Gavin Bonshor on December 17, 2018 12:30 PM EST- Posted in

- Motherboards

- Intel

- Killer

- MSI

- Coffee Lake

- i7-8700K

- Z390

- ACE

- Z390 ACE

CPU Performance, Short Form

For our motherboard reviews, we use our short form testing method. These tests usually focus on if a motherboard is using MultiCore Turbo (the feature used to have maximum turbo on at all times, giving a frequency advantage), or if there are slight gains to be had from tweaking the firmware. We put the memory settings at the CPU manufacturers suggested frequency, making it very easy to see which motherboards have MCT enabled by default.

For Z390 we are running an updated version of our test suite, including OS and CPU cooler. This has some effect on our results.

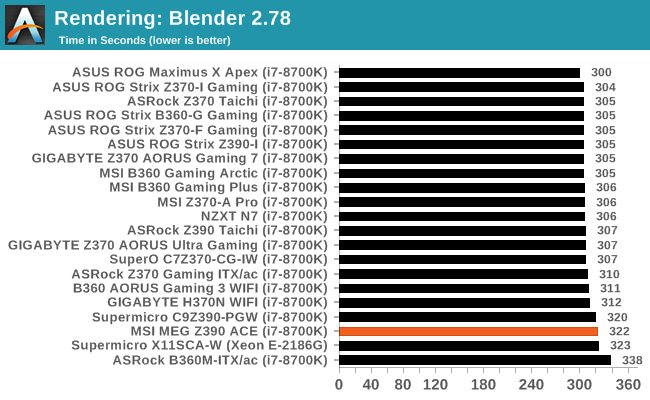

Rendering - Blender 2.78: link

For a render that has been around for what seems like ages, Blender is still a highly popular tool. We managed to wrap up a standard workload into the February 5 nightly build of Blender and measure the time it takes to render the first frame of the scene. Being one of the bigger open source tools out there, it means both AMD and Intel work actively to help improve the codebase, for better or for worse on their own/each other's microarchitecture.

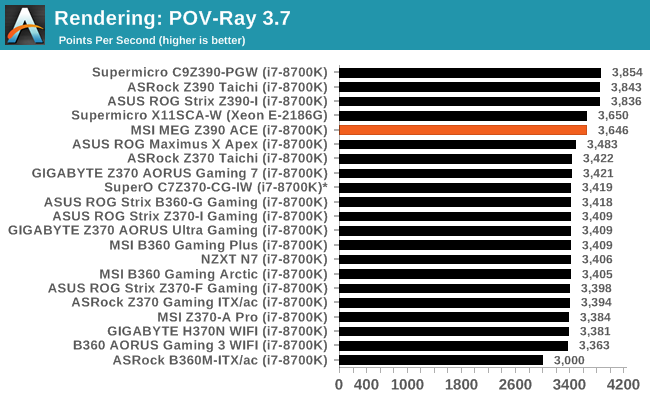

Rendering – POV-Ray 3.7: link

The Persistence of Vision Ray Tracer, or POV-Ray, is a freeware package for as the name suggests, ray tracing. It is a pure renderer, rather than modeling software, but the latest beta version contains a handy benchmark for stressing all processing threads on a platform. We have been using this test in motherboard reviews to test memory stability at various CPU speeds to good effect – if it passes the test, the IMC in the CPU is stable for a given CPU speed. As a CPU test, it runs for approximately 1-2 minutes on high-end platforms.

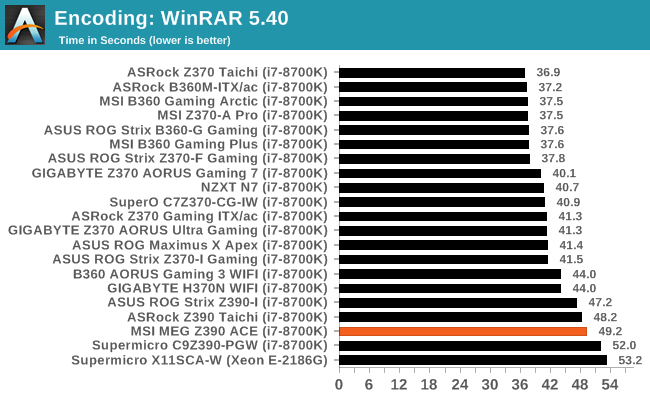

Compression – WinRAR 5.4: link

Our WinRAR test from 2013 is updated to the latest version of WinRAR at the start of 2014. We compress a set of 2867 files across 320 folders totaling 1.52 GB in size – 95% of these files are small typical website files, and the rest (90% of the size) are small 30-second 720p videos.

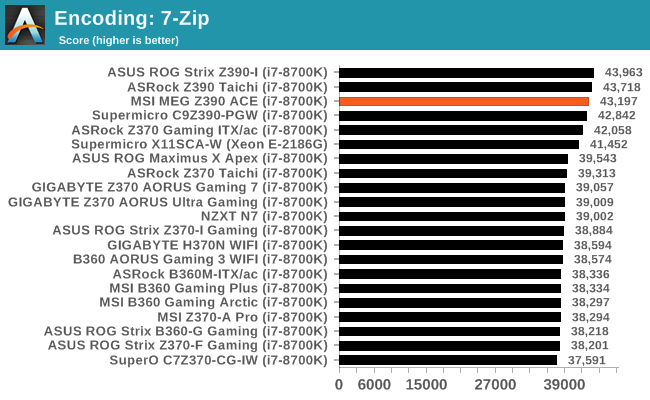

Synthetic – 7-Zip 9.2: link

As an open source compression tool, 7-Zip is a popular tool for making sets of files easier to handle and transfer. The software offers up its own benchmark, to which we report the result.

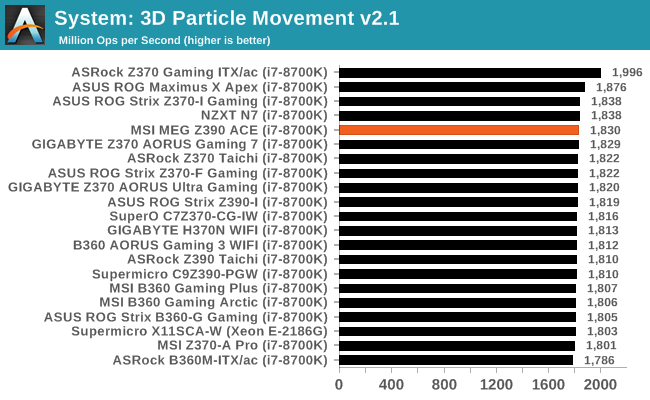

Point Calculations – 3D Movement Algorithm Test: link

3DPM is a self-penned benchmark, taking basic 3D movement algorithms used in Brownian Motion simulations and testing them for speed. High floating point performance, MHz, and IPC win in the single thread version, whereas the multithread version has to handle the threads and loves more cores. For a brief explanation of the platform agnostic coding behind this benchmark, see my forum post here.

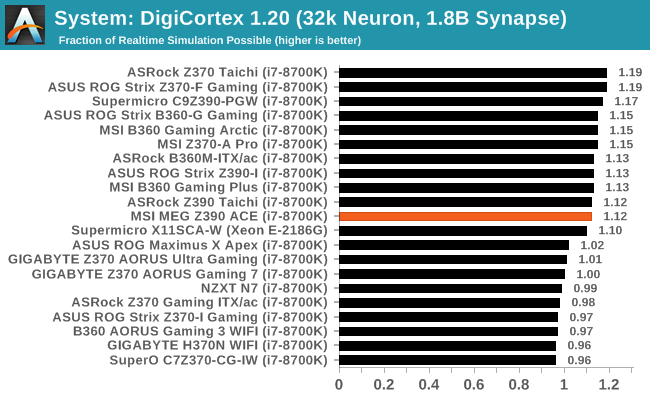

Neuron Simulation - DigiCortex v1.20: link

The newest benchmark in our suite is DigiCortex, a simulation of biologically plausible neural network circuits, and simulates activity of neurons and synapses. DigiCortex relies heavily on a mix of DRAM speed and computational throughput, indicating that systems which apply memory profiles properly should benefit and those that play fast and loose with overclocking settings might get some extra speed up. Results are taken during the steady-state period in a 32k neuron simulation and represented as a function of the ability to simulate in real time (1.000x equals real-time).

25 Comments

View All Comments

rsandru - Monday, December 17, 2018 - link

We're almost in 2019, can we move on beyond those 16 + 4 PCI-E lanes for the CPU please?I just want my GPU and M.2 storage connected directly to the CPU and not sharing bandwidth and latency with a million USB, SATA or audio ports and other traffic on the DMI uplink...

DanNeely - Monday, December 17, 2018 - link

I'd not hold my breath. Adding more PCIe lanes to the CPU would drive up die sizes and board costs for the >90% of systems that don't have a GPU.The only way I could see that happen is if Intel takes the CPU on Chipset stacking concept they showed at manufacturing day beyond the mobile demo to the desktop. Even then, I'd expect what they'd do is 16PCIe + ~8 configurable HSIO lanes so that entry level desktops could have 3-5x USB3, a 4/2 lane PCIe SSD and onboard wifi; either without needing a separate chip; or only with a tiny superbare bone chip to handle all the ultra-legacy and low bandwidth connections needed to control assorted chips on the board behind the scenes.

With that being a new manufacturing process though, I wouldn't expect to see it in the next year or two on the high volume mainstream desktop platform. Far more likely would be for it to launch as a premium option for top end laptop makers in the next year or two that trickles down over the to the rest of the market 2 or 4 years later.

DigitalFreak - Monday, December 17, 2018 - link

I agree, but the Intel/AMD response would be that you should look at HEDT / Threadripper if you need more CPU PCI-E lanes.Ryzen CPUs actually have 32 PCI-E lanes on the CPU, but the socket AM4 is only designed to for 16 GPU + 4 NVME + 4 to the SB. The other 8 aren't used. No idea why they didn't design AM4 to use all of them, unless it was for backwards compatibility with the pre-Ryzen CPUs.

DanNeely - Monday, December 17, 2018 - link

The problem is that both companies big socket platforms are a lot more expensive; and 90% of it is for things that are irrelevant to the average enthusiast; while both companies mainstream sockets fall a little bit short. Intel's by forcing SSDs into the DMI bottleneck; AMD's just in that their current chipset is a more or less obsolete piece of junk (eg only supporting PCIe 2.0). A combination of AMD's 20 non chipset lanes and a chipset approaching what Intel's are capable of would cover most of the gap between the mainstream platforms and enthusiast goals without going the budget busting route of the big sockets.Dunno that AMD's ever spoken about the unused 8 lanes. Could be cost reasons (would've made boards more expensive for legacy platforms); or even just to limit forward compatibility/confusion issues like the garbage fire Intel created when they had an LGA20xx generation that could have 16, 28, or 44 PCIe lanes and board makers either had to add a lot of extra complexity, have large chunks non-operational if using a low lane count chip, or ignore the potential of a number of lanes on the higher end chips.

namechamps - Monday, December 17, 2018 - link

It is backward compatibility. At this point one would think manufacturers would break that backwards compatibility (i.e. 2nd and 3rd m.2 slots not available for non-Ryzen processors).philehidiot - Monday, December 17, 2018 - link

So, please clarify this for someone who is not a computer scientist and is mildly drunk... if I buy a new Ryzen CPU, thinking I'm going to get 24 PCI-E lanes, I will in truth only be able to access 16, same as Intel? Or is it that I'd be able to access 24 whilst the CPU is designed for 32?DanNeely - Monday, December 17, 2018 - link

You can effectively use 20 lanes. The last 4 are used to connect the chipset on any but the lowest end boards which the CPU operate in SoC mode (and which probably will ignore the last 4 lanes entirely to save costs).tvanpeer - Monday, December 17, 2018 - link

Sure you can: get an AMD CPU.shaolin95 - Monday, December 24, 2018 - link

Sure and then get a performance hit. No thanksThe_Assimilator - Monday, December 17, 2018 - link

Congratulations, you're among a tiny minority of users. If you really want or need that feature, pony up the cash to step up to the HEDT segment.